关键词: 电路设计, 工作原理

问:如何在不减慢断开速度的情况下减慢FET的导通速度?

作为电路设计人员,你可能会遇到这样一种情况:需要使用串联栅极电阻(如为什么要将电阻与FET的栅极串联中所述)来减慢FET导通的速度,但同时又不希望减慢断开的速度,你将如何做?

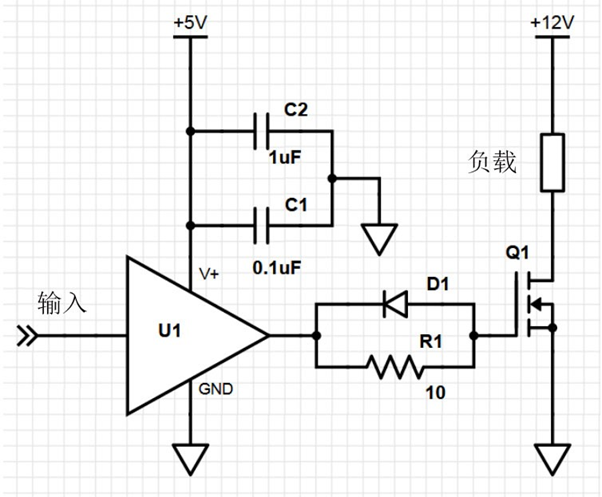

以下述电路图为例,其中使用5V栅极驱动(U1)来打开/关闭用于切换神秘负载的低边N沟道FET。

R1用于减慢FET的导通速度。FET的栅极电容中充满了电流(其峰值被10Ω电阻限制为500mA(5V/10Ω)),栅极电压将随着R1设置的时间常数和Q1的栅极电容(大约值)上升。上升到FET阈值电压所需的时间为导通时间,那断开时间又怎么办呢?

在没有任何其他干预的情况下,断开时间与导通时间大致相同,因为FET的栅极电容也必须通过R1放电。不过,添加标示极性的二极管D1可以缩短断开时间,但不会缩短故意延长的导通时间。

需要注意的是,目前的栅极电压在断开状态下包含一个额外的二极管电压降,但只要该电压远低于FET阈值电压即可完全断开,无需担心。另请注意,如果需要相反的效果(即快速导通,缓慢断开),只需在相同概念上反转二极管的极性即可(类似地,导通电压的二极管电压降仍必须远高于FET阈值电压,才能完全导通)。

一种可能需要用到此种方法的应用是具有高边和低边FET的桥式驱动电路:其中,一个FET必须在导通另一个FET之前完全断开,以避免直通(在两个FET同时短暂导通时,电源通过二者对GND暂时短路)。

更多电路设计相关的技术信息, 请参阅:

———————————————————–

如有任何问题,欢迎联系得捷电子Digi-Key客服团队。

中国(人民币)客服

- 400-920-1199

- service.sh@digikey.com

- QQ在线实时咨询 |QQ号:4009201199

中国(美金)/ 香港客服

- 400-882-4440

- 8523104-0500

- china.support@digikey.com

到微信搜寻“digikey”或“得捷电子”

关注我们官方微信

并登记成会员,

每周接收工程师秘技,

赚积分、换礼品、享福利